DOI: https://doi.org/10.34680/2076-8052.2021.4(125).15-18

## СПОСОБ ПОВЫШЕНИЯ ПОРОГОВОГО НАПРЯЖЕНИЯ КРЕМНИЕВЫХ ДМОП-ТРАНЗИСТОРОВ

В.В.Гаврушко, В.А.Ласткин\*, Т.А.Фирсова\*

## METHOD FOR INCREASING THRESHOLD VOLTAGE OF SILICON DMOS TRANSISTORS

## V.V.Gavrushko, V.A.Lastkin\*, T.A.Firsova\*

Новгородский государственный университет имени Ярослава Мудрого, Gawrushko@mail.natm.ru \*OAO «ОКБ-Планета», Великий Новгород, LastkinVA@okbplaneta.ru

Исследовано влияние концентрации примеси в подложке и типа легирующей примеси поликремниевого затвора на пороговое напряжение кремниевых ДМОП-транзисторов с индуцированным *п*-каналом. Показано, что увеличение средней концентрации примеси в подложке на 50% позволило повысить пороговое напряжение транзистора более чем на 30%. Однако при этом наблюдался рост сопротивления канала транзистора, что повлекло за собой уменьшение тока стока примерно на 25%. Установлено влияние типа проводимости поликремниевого затвора на величину порогового напряжения транзистора. Показано, что замена фосфора на бор при легировании поликремниевого затвора позволяет увеличить пороговое напряжение примерно на 25%. При этом ток стока транзисторов не изменялся, что может представлять практический интерес при разработке помехозащищенных ключей на полевых транзисторах.

Ключевые слова: ДМОП-транзистор, индуцированный канал, пороговое напряжение, легирующая примесь, поликремниевый затвор

Для цитирования: Гаврушко В.В., Ласткин В.А., Фирсова Т.А. Способ повышения порогового напряжения кремниевых ДМОП-транзисторов // Вестник НовГУ. Сер.: Технические науки. 2021. №4(125). С.15-18. DOI: https://doi.org/10.34680/2076-8052.2021.4(125).15-18

The effect of the impurity concentration in the substrate and the type of dopant in a polysilicon gate on the threshold voltage of silicon DMOS transistors with an induced n-channel has been investigated. It is shown that an increase in the average impurity concentration in the substrate by 50% makes it possible to increase the threshold voltage of the transistor by more than 30%. However, at the same time, an increase in the resistance of the transistor channel is observed, which entails a decrease in the drain current by about 25%. The influence of the conductivity type of the polysilicon gate on the threshold voltage of the transistor has been determined. It is shown that replacing phosphorus with boron when doping a polysilicon gate allows increasing the threshold voltage by about 25%. In this case, the drain current of the transistors does not change, which may be of practical interest in the development of noise-immune switches based on field-effect transistors.

Keywords: DMOS transistor, induced channel, threshold voltage, doping impurity, polysilicon gate

For citation: Gavrushko V.V., Lastkin V.A., Firsova T.A. Method for increasing the threshold voltage of silicon DMOS transistors // Vestnik NovSU. Issue: Engineering Sciences. 2021. №4(125). P.15-18. DOI: https://doi.org/10.34680/2076-8052.2021.4(125).15-18

МДП-транзисторы находят широкое применение в современной энергетической электронике. Главные области применения мощных МДП-транзисторов — электрические приводы переменного тока, преобразователи частоты для электротехнических установок, источники вторичного электропитания и т. п. [1]. По сравнению с другими полупроводниковыми приборами, такими как биполярные транзисторы и тиристоры, они обладают малыми временами переключения (1-10 нс против 1 мкс у биполярных приборов) и вследствие этого малыми потерями на переключение, а также характеризуются более высокими рабочими напряжениями и температурами.

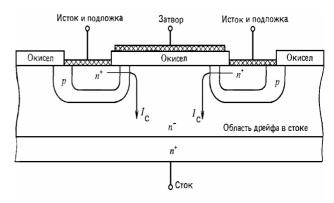

Наибольшую популярность среди МДП-транзисторов получили транзисторы с каналом n-типа в силу большей подвижности носителей заряда в канале. Среди них в последнее время в качестве эффективных ключей хорошо зарекомендовали себя вертикальные ДМДП-структуры (или ДМОП-транзисторы), где сток транзистора находится с обратной стороны кристалла (рис.1). Канал в таких транзисторах создаётся методом двойной диффузии в одно и то же окно: сначала формируется p-карман (подложка), а затем  $n^+$ -карман (область истока) [2]. Как видно из рис.1,

ток внутри ДМОП-транзистора сначала протекает горизонтально, а затем вертикально — по эпитаксиальному слою (области дрейфа) стока. Современные ДМОП-структуры имеют многоячеистую (многоканальную) конструкцию, где каждая ячейка представляет собой отдельный элементарный полевой транзистор. Все ячейки соединяются между собой параллельно алюминиевой металлизацией.

Рис.1. Вид поперечного сечения элементарной ячейки вертикального ДМДП-транзистора с n-каналом

Как показано на рис.1, канал транзистора образуется в зазоре между двумя карманами p- и n<sup>+</sup>-типа путём подачи положительного напряжения на поликремниевый затвор, который лежит непосредственно на тонком подзатворном диэлектрике. При этом ток в канале появляется только при подаче на затвор определённого значения напряжения, которое называется пороговым.

Пороговое напряжение является одним из важнейших электрических параметров полевых транзисторов. При подаче порогового напряжения  $U_{\mathrm{nop}}$  на затвор в р-кармане (подложке) возникает инверсия при выполнении условия [3]:

$$\Phi_{\text{ron}} = 2\Phi_{\text{F}}$$

$\Phi_{\rm nob} = 2\Phi_{\it F},$  где  $\Phi_{\rm nob}$  — поверхностный потенциал, являющийся мерой изгиба энергетических зон, и представляет собой потенциал на кремнии у поверхности, измеренный от уровня Ферми  $E_i$  в собственном кремнии;  $\Phi_{F}$  — потенциал Ферми.

Выражение для порогового напряжения МОПтранзистора имеет вид [4]:

$$U_{\text{\pi op}} = \varphi_{\text{MII}} + \frac{q \cdot d_{\text{SiO}_2} (N_a X_d - N_{nc})}{\varepsilon_{\text{SiO}_2} \cdot \varepsilon_0} + 2\varphi_F, \quad (*)$$

где  $N_{nc}$  — плотность поверхностных состояний;  $X_d = \left(\frac{\varepsilon_{\mathrm{Si}} \times \varepsilon_0 \times 2\phi_F}{qN_a}\right)^{1/2}$  — ширина обеднённого слоя;  $\phi_F = \frac{kT}{a} \ln N_a / n_i$  — встроенный потенциал подложки;  $N_a$  — концентрация примеси в подложке;  $\phi_{\rm MII}$ — разность работ выхода материалов затвор — подложка, в *п*-канальном транзисторе имеет значение:

$$\phi_{

m M\Pi}$$

= -0,6 -  $\phi_F$  (для Al затвора),  $\phi_{

m M\Pi}$  =  $-\frac{\phi_g}{2}$  -  $\phi_F$

(для затвора из *n*-поликремния);  $\phi_{\rm M\Pi} = + \frac{\phi_g}{2} - \phi_F$ (для затвора из p-поликремния);  $\phi_g$  — потенциал, определяемый шириной запрещённой зоны кремния.

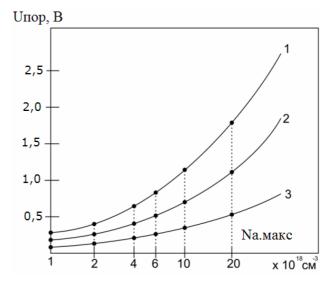

При работе в ключевом режиме в различных логических схемах зачастую требуется, чтобы транзистор не срабатывал до определённого значения напряжения на затворе (например, вследствие наличия помех). Как видно из выражения (\*), повышения порогового напряжения можно достичь увеличением толщины подзатворного диэлектрика  $(d_{\mathrm{SiO}_2})$  или увеличением концентрации примеси в подложке  $(N_a)$ . Примеры зависимости порогового напряжения некоторых полевых транзисторов от концентрации примеси в подложке при различной толщине подзатворного диэлектрика показаны на рис.2 [4].

Из рис.2 видно, что с увеличением толщины подзатворного диэлектрика или концентрации примеси в р-кармане значительно увеличивается пороговое напряжение. Однако увеличение концентрации примеси в подложке транзистора приводит к уменьшению подвижности носителей в канале, что в свою очередь приводит к уменьшению тока стока. Аналогично, если увеличить толщину подзатворного диэлектрика, то напряжённость электрического поля в диэлектрике уменьшится, что приведёт к уменьшению концентрации носителей в индуцированном канале и, как следствие, нежелательному падению тока стока.

Рис.2. Пороговое напряжение  $U_{\text{пор}}$  как функция  $N_{a \text{ max}}$  в области канала при толщине оксида в канале: 0,3 мкм (кривая 1), 0,2 мкм (кривая 2) и 0,1 мкм (кривая 3) [4]

Одним из интересных вариантов увеличения порогового напряжения является изменение типа проводимости поликремниевого затвора [5]. Так, для создания транзистора с п-каналом обычно используют  $n^+$ -поликремниевый затвор, легированный фосфором. При этом если легировать поликремниевый затвор бором (примесью р-типа), то изменение энергетической диаграммы поверхности приведёт к увеличению работы выхода из поликремниевого затвора, что в свою очередь позволит увеличить пороговое напряжение [3].

В соответствии с выражением (\*), для порогового напряжения транзисторов с поликремниевым

затвором *n*- и *p*-типа проводимости можно записать:

$$U_{\text{пор\_}n} = -\frac{\phi_g}{2} + \frac{q \cdot d_{\text{SiO}_2}(N_a X_d - N_{nc})}{\epsilon_{\text{SiO}_2} \cdot \epsilon_0} + \phi_F,$$

для

$$n$$

-поликремниевого затвора;

$$U_{\text{пор\_}p} = \frac{\phi_g}{2} + \frac{q \cdot d_{\text{SiO}_2}(N_a X_d - N_{nc})}{\epsilon_{\text{SiO}_2} \cdot \epsilon_0} + \phi_F,$$

для р-поликремниевого затвора.

Отсюда следует, что разница  $U_{\text{пор }p} - U_{\text{пор }n} =$  $= \phi_g \approx 1.1 \, \mathrm{B}.$  Таким образом, если в качестве затвора вместо  $n^+$ -поликремния использовать  $p^+$ -поликремний, то в идеальном случае пороговое напряжение транзистора может вырасти на 1,1 В. Однако следует учесть, что на его величину могут влиять уровни легирования поликремниевого затвора и подложки, а также другие факторы, определяемые технологией прибора [3].

С целью проверки возможности повышения порогового напряжения были изготовлены транзисторы с разным типом проводимости поликремниевого затвора, которые формировались на эпитаксиальных  $n-n^+$ -структурах кремния с ориентацией кристал-

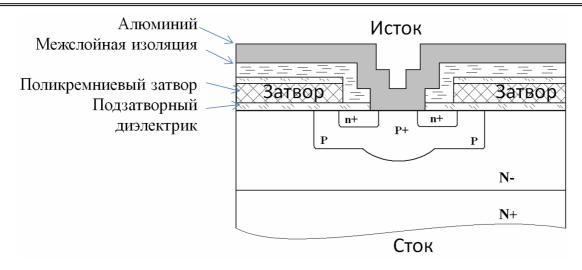

Рис.З. Поперечное сечение элементарной ячейки изготовленных ДМОП-транзисторов с каналом *п*-типа

лографических осей <111>, с удельным сопротивлением эпитаксиальной плёнки 6–8 Ом см и толщиной около 30 мкм. Для опытных партий были изготовлены транзисторы с разным уровнем легирования подложки.

На рис.3 изображен эскиз поперечного сечения элементарной ячейки изготовленных транзисторов с индуцированным *п*-каналом. Карман *p*-типа (подложка транзистора) был образован ионной имплантацией бора с последующей разгонкой на глубину порядка 4.0 мкм. Здесь транзисторы были поделены на две группы: после ионной имплантации и разгонки слоевое сопротивление подложки (р-области) транзисторов первой группы составило около 300 Ом/□, второй около 400 Ом/□. Карман  $n^+$  образован диффузией фосфора на глубину около 0,6 мкм и слоевым сопротивлением около 15 Ом/□ и служил истоком транзистора. Диффузия фосфора осуществлялась в те же окна, что и ионное легирование бора (р-карман), это позволило осуществить операцию самосовмещения канала транзистора.

Для улучшения омического контакта с p-областью и уменьшения влияния вертикального паразитного биполярного  $n^+$ -p- $n^-$ - $n^+$ -транзистора в центр транзисторных ячеек проводилась диффузия бора на глубину 2,0 мкм и слоевым сопротивлением около 40-70 Ом/ $\square$  ( $p^+$ -карманы, формирование так называемых «истоковых перемычек» [6]). Одновременно с помощью данной диффузии бора с целью увеличения напряжения лавинного пробоя транзисторов [7] формировались охранные кольца по периферии центральной (активной) части кристалла.

В качестве подзатворного диэлектрика транзистора использовалась комбинация пленок  $SiO_2$ - $Si_3N_4$ . При этом плёнка нитрида кремния осуществляла пассивирующую функцию. Пленка  $SiO_2$  выращивалась в атмосфере сухого кислорода при температуре  $1050^{\circ}$ С. Пленка нитрида кремния осаждалась методом взаимодействия газов моносилана и аммиака при температуре  $850^{\circ}$ С. Пленка поликристаллического кремния толщиной около 0,5 мкм, выполняющая роль затвора, осаждалась поверх затворного диэлектрика методом разложения моносилана при температуре  $630^{\circ}$ С. Для

уменьшения сопротивления затвора в плёнку поликристаллического кремния проводилась диффузия примеси.

Было сформировано две опытные партии. В первой легирование поликремния осуществлялось фосфором при различной концентрации примеси в подложке. Во второй партии поликремниевый затвор легировался фосфором или бором при одинаковой концентрации примеси в подложке.

Конфигурация поликремниевого затвора в центральной части кристалла между транзисторными ячейками формировалась фотолитографией с последующим плазмохимическим вытравлением поликремния в плазме СF<sub>4</sub> в ненужных областях над ячейками и по периферии кристалла. Изоляция между электродами истока и поликремниевым затвором осуществлялась последовательным осаждением диэлектрических плёнок Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub> с последующим вытравливанием контактных окон к транзисторным ячейкам и поликремниевому затвору. Далее поверх сформированного изолятора напылялась плёнка алюминия толщиной 1-1,4 мкм вакуумнотермическим способом с последующим формированием электродов истока (объединяющего все транзисторные ячейки) и затвора. Для контакта к стоку на обратную сторону пластины напылялась система металлизации Ti-Ni-Au и осаждалось гальваническое золото толщиной 3-4 мкм. Размеры кристаллов транзисторов составили  $1,8\times0,8$  мм<sup>2</sup>.

По завершении технологического цикла проводились измерения электрических характеристик транзисторов на измерителе параметров полупроводниковых приборов Л2-56. Контролируемыми параметрами являлись: напряжение лавинного пробоя транзисторов в режиме:  $U_{\rm 3H}=0$  В,  $I_{\rm c}=10$  мкА; ток стока транзисторов в режиме:  $U_{\rm 3H}=3.5$  В,  $U_{\rm cH}=0.5$  В; и пороговое напряжение транзисторов в режиме:  $U_{\rm 3H}=U_{\rm CH}$ ;  $I_{\rm c}=1.0$  мА.

В табл.1 приведены результаты измерений электрических параметров транзисторов первой партии с различной концентрацией примеси бора в p-кармане (подложке). Средняя концентрация примеси в подложке была определена согласно кривым Ирвина [8].

Таблица 1 Результаты измерений электрических параметров транзисторов с различной концентрацией примеси в подложке

| Транзисторы<br>Параметры                                                    | Группа 1          | Группа 2          |

|-----------------------------------------------------------------------------|-------------------|-------------------|

| $R_s$ , Ом/ $\square$                                                       | 304–316           | 402–412           |

| $\overline{N_a}$ , cm <sup>-3</sup>                                         | $3,7\cdot10^{17}$ | $2,4\cdot10^{17}$ |

| $I_{c, MA}$<br>( $U_{cu} = 0.5 \text{ B}; U_{3u} = 3.5 \text{ B}$ )         | 85–90             | 105–115           |

| $U_{ m проб}$ , В                                                           | 260–275           | 260–275           |

| $U_{\text{зи пор}}, B$ $(U_{\text{си}} = U_{\text{зи}}; Ic = 1 \text{ мA})$ | 1,5–1,6           | 1,1-1,2           |

Из табл.1 видно, что увеличение концентрации примеси в подложке примерно в 1,5 раза действительно привело к увеличению порогового напряжения с 1,1–1,2 В до 1,5–1,6 В. Однако при этом наблюдалось негативное снижение тока стока транзисторов в среднем на 25% вследствие уменьшения подвижности носителей заряда в канале.

В табл.2 представлены результаты измерений электрических параметров транзисторов с разным типом проводимости поликремниевого затвора.

Таблица 2 Параметры транзисторов с различным типом проводимости поликремниевого затвора

| Транзисторы                                                                     | c n <sup>+</sup> - | c p <sup>+</sup> -   |

|---------------------------------------------------------------------------------|--------------------|----------------------|

|                                                                                 | поликремние-       | поликремние-         |

| Параметры                                                                       | вым затвором       | вым затвором         |

| $R_s$ , Om/ $\square$                                                           | 402–412            | 402–412              |

| $\overline{N_a}$ , cm <sup>-3</sup>                                             | $2,4\cdot10^{17}$  | 2,4·10 <sup>17</sup> |

| $I_{c, MA}$<br>( $U_{cH} = 0.5 \text{ B}; U_{3H} = 3.5 \text{ B}$ )             | 105–115            | 105–115              |

| $U_{\text{проб}}$ , В                                                           | 260–275            | 260–275              |

| $U_{3\text{M nop}}$ , B<br>$(U_{\text{CM}} = U_{3\text{M}}; Ic = 1 \text{ MA})$ | 1,1-1,2            | 1,4–1,5              |

Видно, что при легировании поликремниевого затвора бором вместо фосфора пороговое напряжение транзисторов заметно выросло с 1,1-1,2 В до 1,4-1,5 В. При этом падения тока стока транзисторов не наблюдалось. В отличие от первого варианта, где пороговое напряжение было повышено за счет увеличения уровня легирования подложки, в данном варианте повышение порогового напряжения благодаря увеличению работы выхода из материала затвора не приводило к снижению подвижности носителей заряда в канале.

Таким образом, использование в *n*-канальных транзисторах в качестве затвора плёнок поликристаллического кремния *p*-типа проводимости позволяет получать более высокие значения порогового напря-

жения без увеличения сопротивления канала транзистора. Это может быть полезным в логических ключевых схемах при необходимости противодействия срабатыванию транзистора от воздействия ложных помех.

- 1. Довгун В.П. Электротехника и электроника: учеб. пособие. В 2-х ч. Ч. 2. Красноярск: ИПЦ КГТУ, 2006. 252 с.

- 2. Окснер Э.С. Мощные полевые транзисторы и их применение / Пер. с англ. М.: Радио и связь, 1985. 288 с.

- 3. Блихер А. Физика силовых биполярных и полевых транзисторов / Пер. с англ. Л.: Энергоатомиздат, 1986. 248 с.

- 4. Колосницын Б.С., Гапоненко Н.В. Полупроводниковые приборы и элементы интегральных микросхем: учеб. пособие. В 2-х ч. Ч.2: Расчет и проектирование полевых транзисторов. Минск: БГУИР, 2012. 96 с.

- Мустафаев Г.А., Кармоков А.М., Мустафаев А.Г. КНИ-КМОП полевые транзисторы с поликремниевыми затворами // Мат. VI Междунар. конф. «Химия твердого тела и современные микро и нанотехнологии». Кисловодск — Ставрополь. Сев-КавГТУ, 2006. 510 с.

- 6. Керенцев А., Ланин В. Конструктивно-технологические особенности MOSFET-транзисторов // Компоненты и технологии. 2007. №4. С.100-104.

- Sze S.M., Gibbons G. Effect of junction curvature on breakdown voltage in semiconductors // Solid-State Electron. 1966. Vol.9. Is.9. P.831-845. DOI: https://doi.org/10.1016/0038-1101(66)90033-5

- Irvin J.C. Resistivity of bulk silicon and of diffused layers in silicon // Bell Syst. Tech. J. 1962. Vol. 41. Is.2. P.387-410. DOI: https://doi.org/10.1002/j.1538-7305.1962.tb02415.x

## References

- Dovgun V.P. Elektrotekhnika i elektronika [Electronics and electrical engineering]. In 2 parts. Part 2. Krasnoyarsk, KSTU Publ., 2006, 252 p.

- Oxner E.S. Power FETs and their applications. Englewood Cliffs, Prentice-Hall, Inc., 1982. (Russ. ed.: Oksner E.S. Moshchnye polevye tranzistory i ikh primenenie. Moscow, "Radio i sviaz" Publ., 1985. 288 p.).

- Blicher A. Field-Effect and Bipolar Power Transistor Physics. New York, Academic Press, 1981. 336 p. (Russ. ed.: Blikher A. Fizika silovykh bipoliarnykh i polevykh tranzistorov. Leningrad, "Energoatomizdat" Publ., 1986. 248 p.).

- Kolosnitsyn B. S. Poluprovodniko-vyye pribory i elementy integral'nykh mikroskhem [Semiconductor devices and elements of integrated circuits]. In 2 parts. Part 2: Raschet i proyektirovaniye polevykh tranzistorov [Calculation and design of field-effect transistors]. Minsk: BSUIR, 2012. 96 p.

- Mustafaev G. A., Karmokov A.M., Mustafaev A. G. KNI-KMOP polevyye tranzistory s polikremniyevy-mi zatvorami [SOI-CMOS Field-effect transistors with polysilicon gates]. Mat. VI Mezhdunar. konf. "Khimiya tverdogo tela i sovremennyye mikro i nanotekhnolo-gii" [6th International Scientific Conference on Solid-State Chemistry and Modern Micro-and Nanotechnologies]. Kislovodsk-Stavropol, NCFU, 2006, 510 p.

- Kerensky A., Lanin V. Konstruktivno-tekhnologicheskiye osobennosti MOSFET-tranzistorov [Design and technological features of MOSFETs]. Komponenty i tekhnologii, no. 4, 2007, pp. 100-104.

- 7. Sze S.M., Gibbons G. Effect of junction curvature on breakdown voltage in semiconductors. Solid State Electronics, 1966, vol. 9, no. 9, pp. 831-845. doi: https://doi.org/10.1016/0038-1101(66)90033-5

- Irvin J.C. Resistivity of bulk silicon and diffused layers in silicon. Bell Syst. Tech. J., 1962, vol. 41, pp. 387-410. doi: https://doi.org/10.1002/j.1538-7305.1962.tb02415.x